路科V0SVP10P12验证环境

验证环境结构

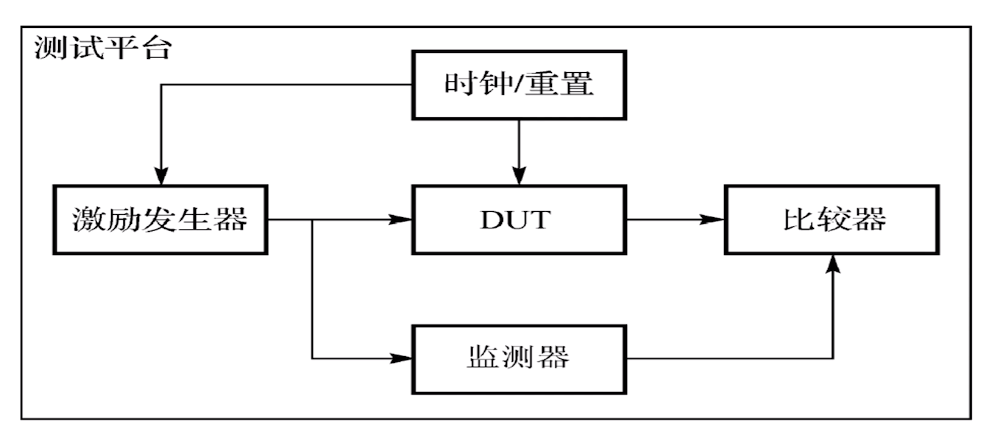

- 测试平台testbench是整个验证系统的总称;

- 包括验证结构中的各个组件、组件之间的连接关系、测试平台的配置和控制

- 还包括编译仿真的流程、结果分析报告和覆盖率量化等;

- 主要关注验证平台的结构和组件部分,他们产生设计需要的各种输入,也会在此基础上进行设计功能检查;

- 各个验证组件相互独立

- 各个验证组件和设计需要互相连接

- 各个验证组件也需要进行通信(线程通信方式)

- 验证环境也需要时钟和复位信号的驱动

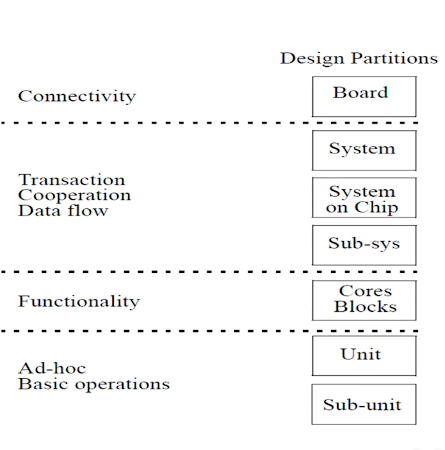

- 设计由多个层次构成,无论是物理分区FPGA/ASIC,还是逻辑分区合成单元/核心子系统;

- 验证也可以按照不同级别安排目标:

- 每个验证级别都有最合适的验证目标

- 较小的模块更容易验证,他们提供了更大的可控性和可观察性;

- 较小的模块容易设置条件和状态组合,观察反应是否符合预期;

- 而他们组成的子系统,以较低的可控性和可观察性为代价;

- 任何层次的待验设计,都应该有稳定的接口和预期功能;

- 理想情况,每个子系统和模块都要有硬件描述文档;

- 如果接口和功能变化,则会影响testbench随之变化,会影响项目进度;

- 对设计稳定性的要求,一般是先接口稳定下来,再功能稳定下来;

硬件设计描述

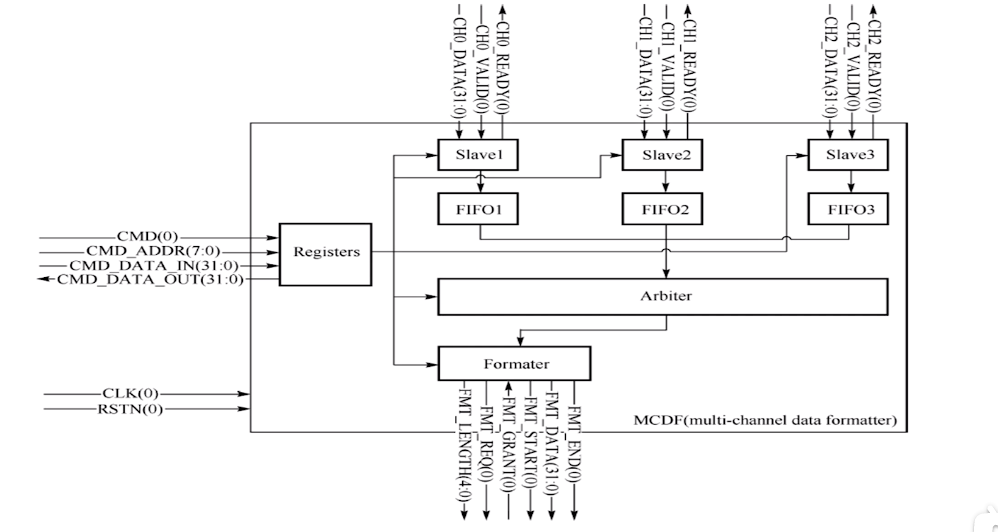

MCDF简介:

- 遵循硬件设计描述的方式,介绍它的结构、功能、寄存器、和时序;

- 多通道数据整形器,可以将上行多个通道数据经过内部的FIFO,最终以数据包的形式送出;

- 上行数据和下行数据的接口协议不同;

- 多通道数据整形器也有寄存器的读写接口,支持更多的控制功能;

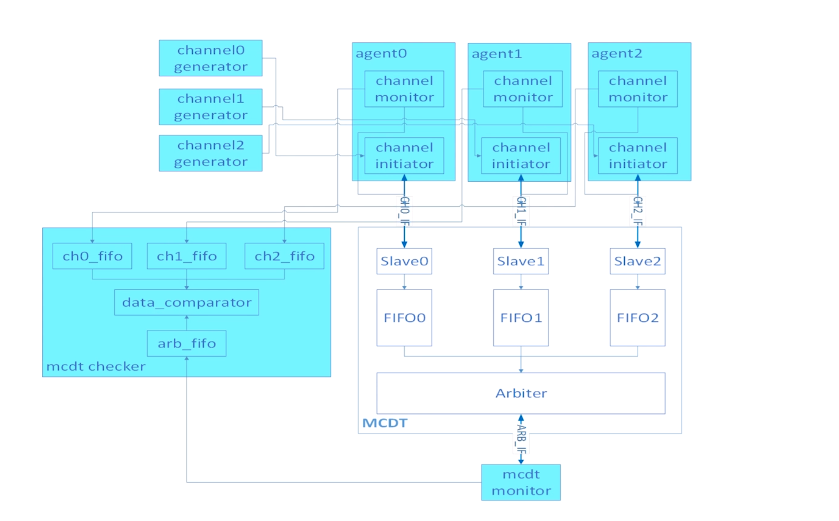

MCDF的结构:

- 通道模块(可以同时接收3路通道的输入数据)

- slave

- FIFO

- 但是由于带宽限制,每个时钟周期只有一路数据可以通过仲裁模块,到达整形器模块!

- 寄存器模块

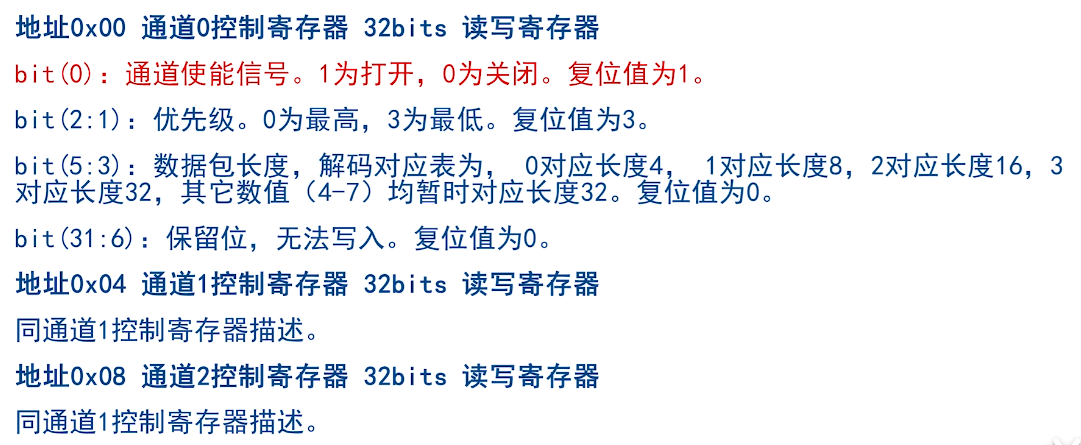

- 控制通道开关

- 控制仲裁器的选择

- 控制整形器打包带长度

- 获取每个通道的FIFO余量

- 仲裁模块

- 整形模块

- 将指定通道的数据重新打包,以新的总线形式发送出去

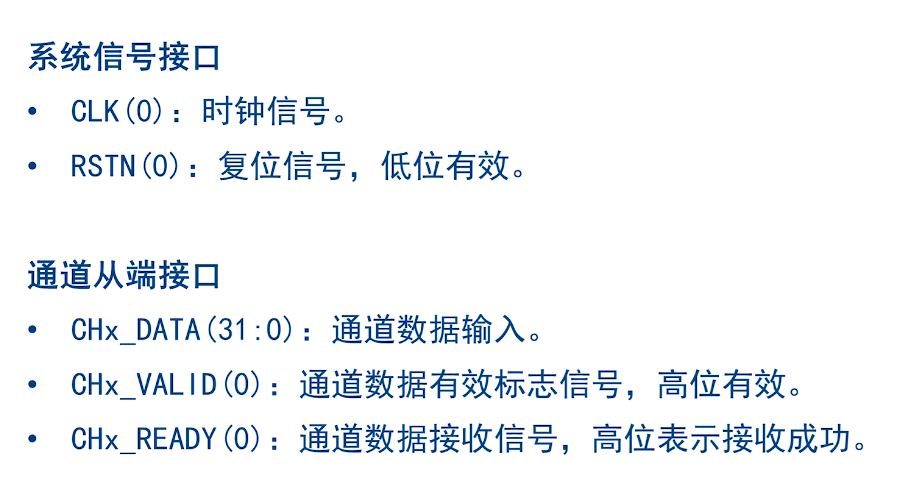

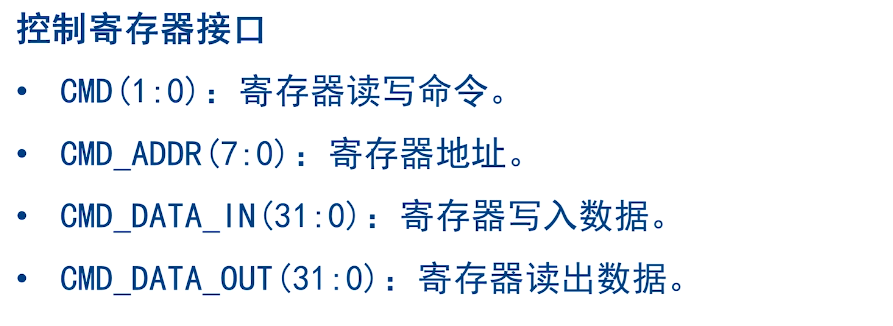

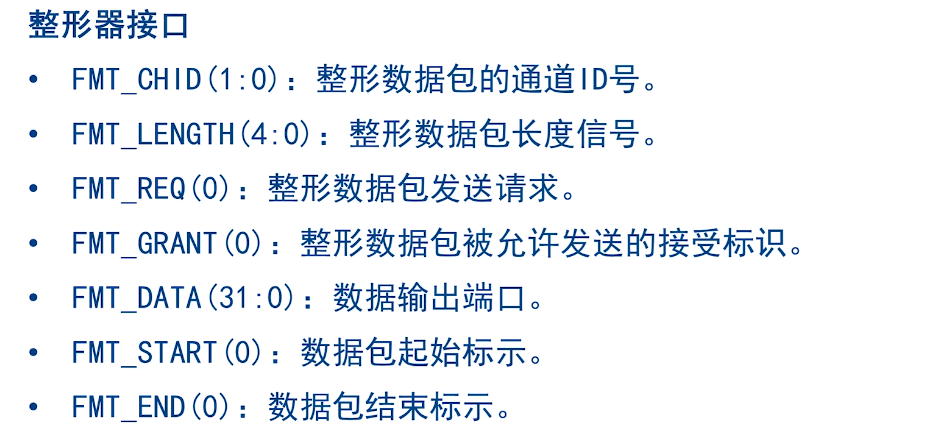

MCDF的接口描述:

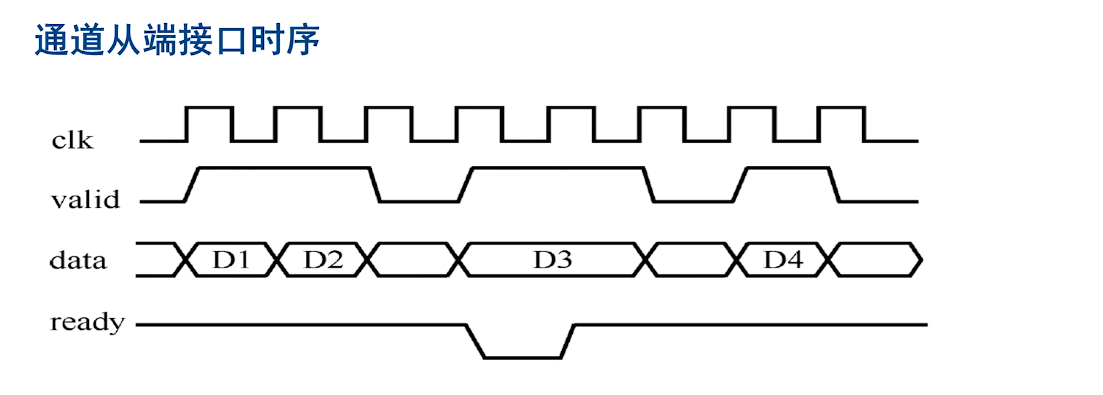

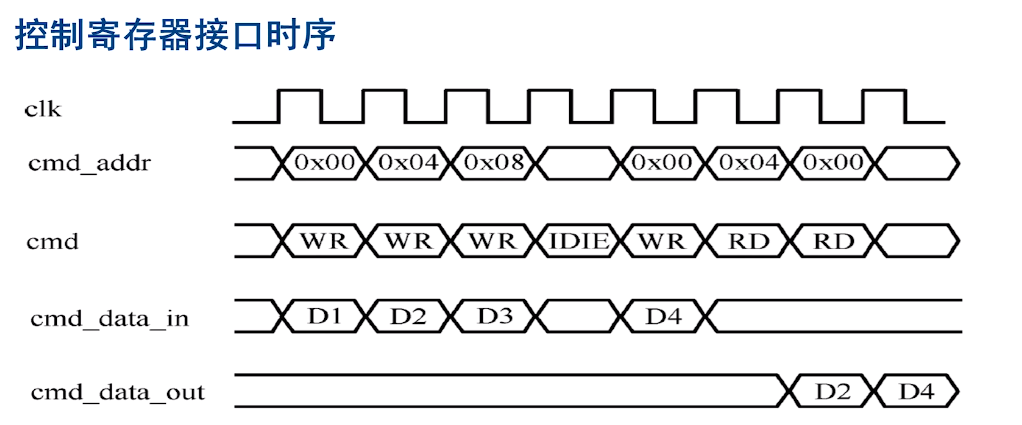

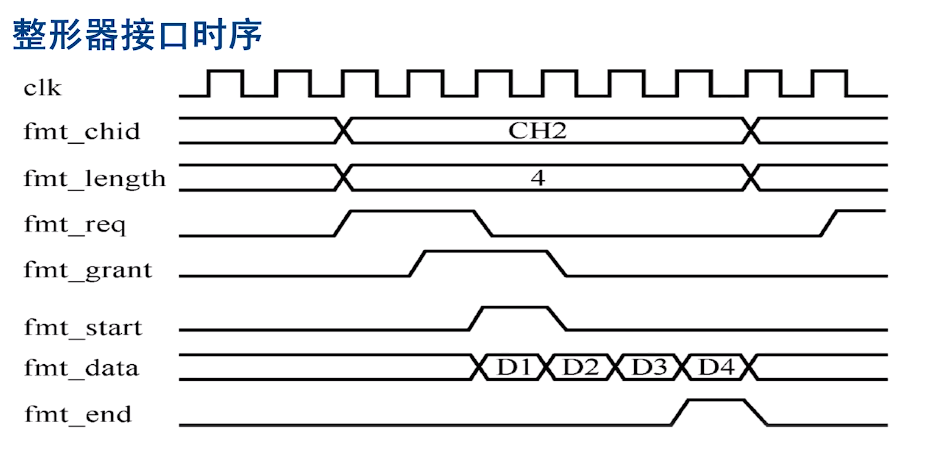

MCDF的接口时序:

- 如果当前周期的valid和ready同时为高,则表示可以发送数据;

- 读写寄存器时,需要给地址端口和指令端口对应的值

- 读取的寄存器数值将在下一个时钟周期由寄存器模块输出

- 当整形器要发送某一个通道的数据时,会拉高req信号,同时也更新chid和长度length信息,等待下行模块接收信号grant为高,其下个周期req应该拉低,同时,start拉高,这时候发送第一个有效数据,发送数据应该连续,发送这段数据的最后一个时,end拉高,start和end的间隔内,data发送完毕!

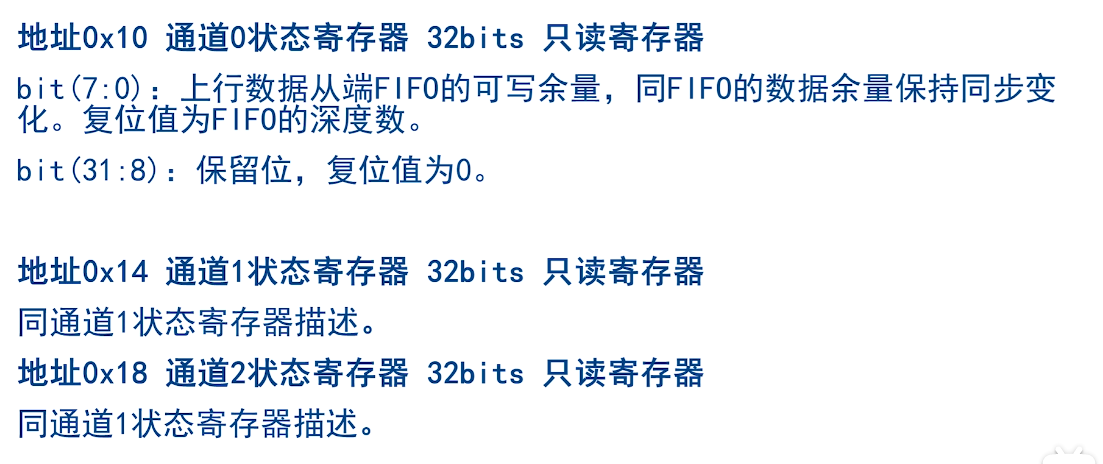

MCDF的寄存器描述:

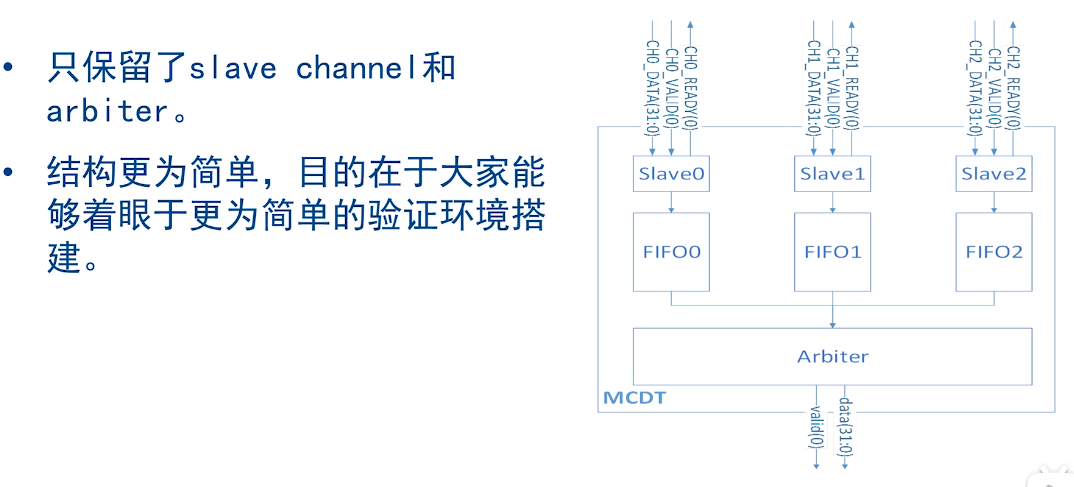

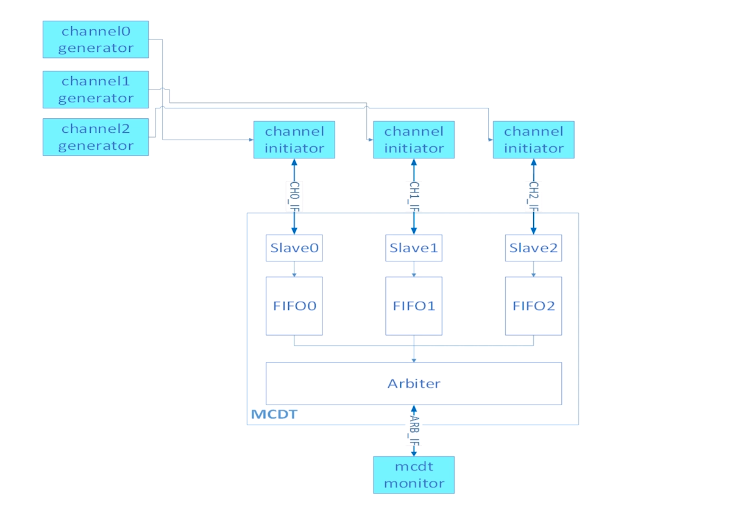

MCDF mini版结构

移除了寄存器模块和整流模块!

功能变成了由多个通道输入,然后仲裁器选择一个通道进行输出。。

验证环境组件

激励发生器

- stimulator(激励发生器):也称为驱动器driver、总线功能模型BFS、行为模型behavioral 或者 发生器generator。

- stimulator的主要职责是模拟与DUT相邻设计的接口协议,只需要关注如何模拟接口信号,使它能够以真实接口协议发送激励给DUT

激励器组件结构

- 按照stimulator和DUT的连接关系,激励发生器分为两种:initiator发起器 和 responder响应器

- 由于channel从端口协议上有握手信号,所以需要遵照接口时序,当chx_ready为低时,保证chx_data和chx_valid保持不变。

- channel initiator 组件:

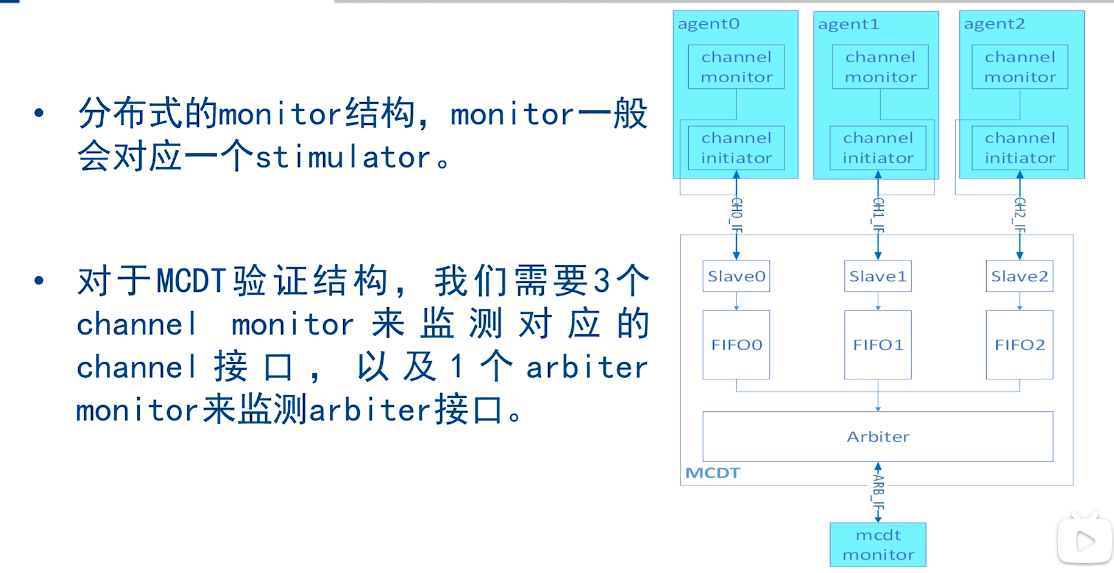

监测器

- monitor(监测器):主要功能是用来观察DUT的边界或者内部信号,并且经过打包整理传送给其他验证平台的组件,比如checker比较器。

- 安装监测信号灯层次划分monitor的功能,分为观测DUT边界信号和观测DUT内部信号。

监测器的组件结构

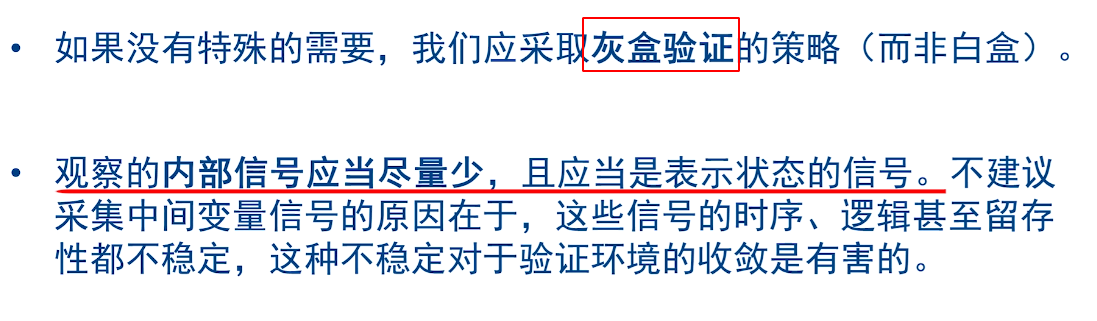

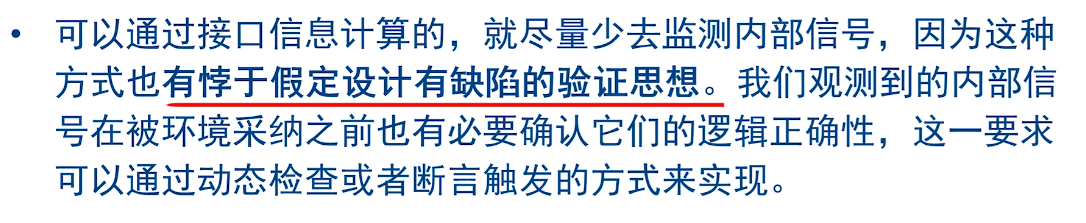

另外一些要求和建议:

比较器

- checker(比较器):投入时间最多的组件,肩负了模拟设计行为和功能检查的任务,而且缓存各个monitor收集到的数据;

- 将DUT输入接口侧的数据汇集给内置的reference model,reference model扮演了模拟硬件功能的角色。

- checker将实际收集到的DUT输出数据和reference model产生的数据进行对比;

- 对于内部设计的关键功能模块,应该有相应的线程进行独立的检查;

- 检查过程中,可以将检查成功的信息统一纳入检查报告中,便于仿真后的追溯,如果检查失败,也可以暂停仿真同时报告错误,在线调试。

- 线上比较:在仿真时收集数据,在线比较,并实时报告。

- 线下比较:仿真时收集的数据记录在文件中,仿真结束后,通过脚本或者其他手段,进行数据比较。

比较器组件结构

比较器实现的建议

路科V0SVP10P12验证环境