数字设计流程

数字设计流程

先放地址,来源于B站比特大陆相关的学习资料。 链接

一、 项目立项

1.1 项目解读

市场、研发、架构、编译器 等相关人员,进行市场需求和竞品分析,初步决定芯片功能、面积、功耗等相关指标。

1.2 技术调研

软件建模、硬件预实现、方案可行性分析等,生成一个市场需求报告。

1.3 开发计划制定

有几个方面会影响到芯片开发的时间线:

- 购买IP,比如PCI接口、DDR等,IP供应商也要时间准备进行定制化开发;

- 代工厂排期;

- 预留研发调试时间;

二、 研发阶段

2.1 技术研讨方案制定

划分芯片的子系统和模块、软硬件工作的划分和规划、各个子系统也要有性能指标定义等。

2.2 详细设计

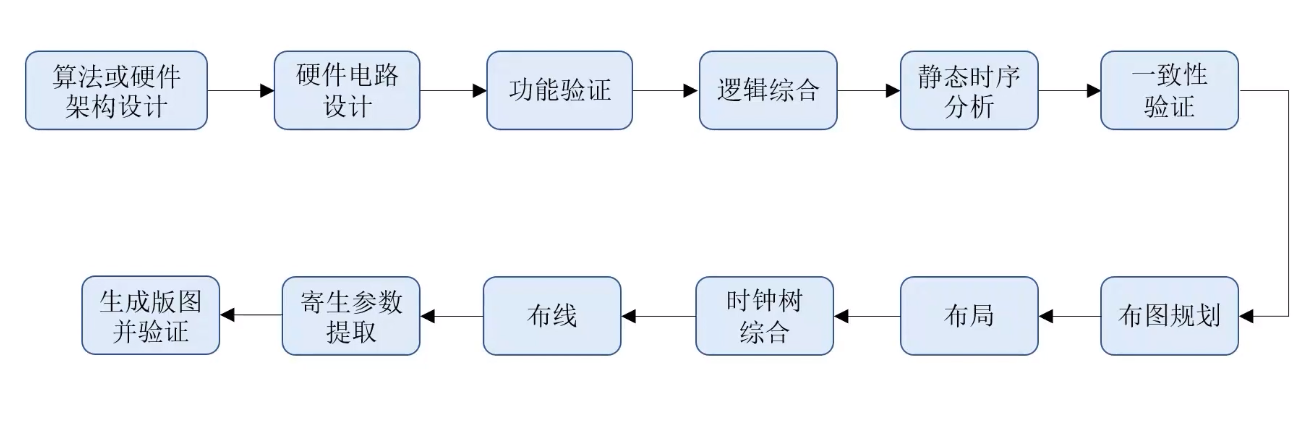

算法和硬件架构、硬件电路设计、功能验证都属于前端设计部分;

逻辑综合、静态时序分析、一致性验证算是中端;

布局布线等等都属于后端;

下面,对这些步骤进行详细介绍:

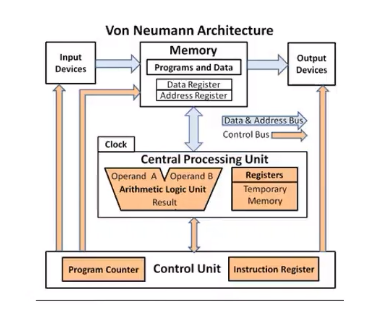

2.2.1 算法和硬件架构设计

- 输入: 功能需求

- 输出: 软件参考模型

- 过程: 架构人员使用Matlab、C++、System C、 System Verilog 等语言工具,完成芯片中数字部分的高层次算法或架构的分析和建模,为硬件提供正确的软件功能模型,更为重要的是,通过大量的高层次仿真和调试,为RTL实现提供总体性的设计指导。越是复杂的数字电路,这部分算法模型仿真越重要。

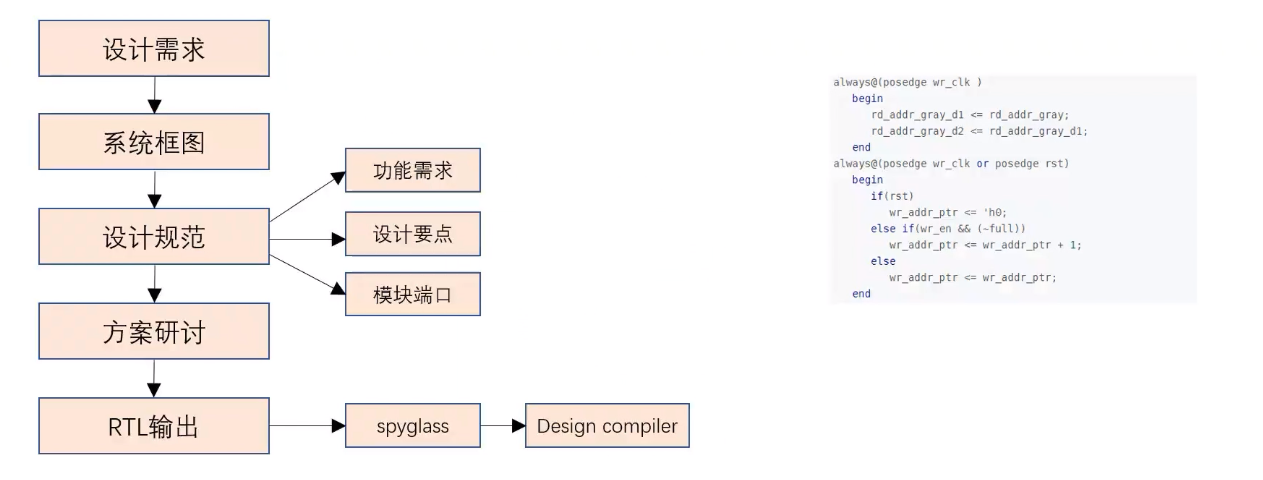

2.2.2 硬件电路设计

- 输入: 从架构拿到的软件参考模型

- 输出: RTL代码、详细的设计文档、逻辑综合报告、语法检查报告

- spyglass: 时序校验、语法校验等

- Design Compiler: 预综合,观察时序面积功耗等是否达到要求;

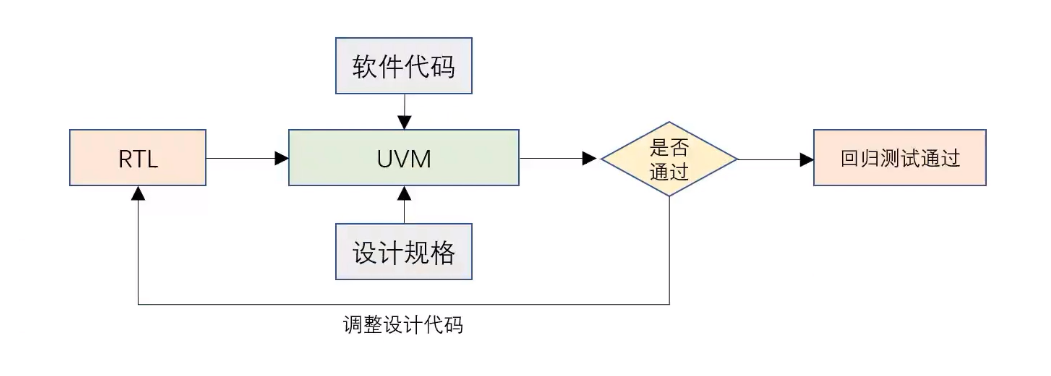

2.2.3 功能验证

- 输入: 设计规格、设计代码、软件模型;

- 输出: 代码覆盖率和功能覆盖率报告;

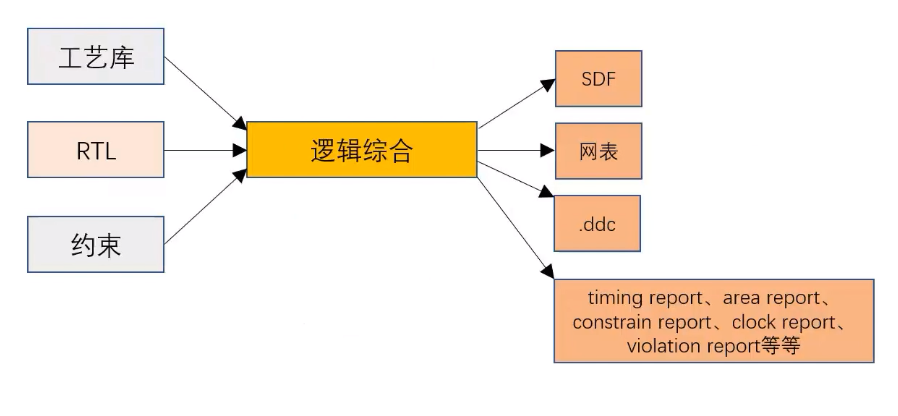

2.2.4 逻辑综合

- 输入: RTL代码、工艺库、约束;

- 输出: 网表、标准延迟文件SDF、工程文件(.ddc)、各类报告;

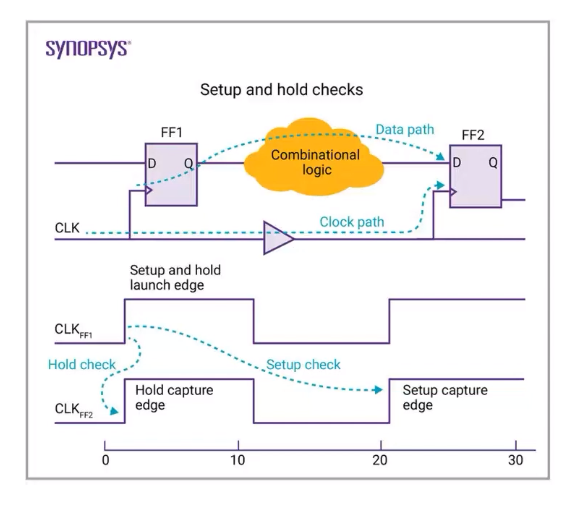

2.2.5 静态时序分析

- 中端人员使用静态时序分析工具 Prime Time,从静态分析角度,保证设计中所有的路径,满足内部时序单元对建立时间和保持时间的要求。

- 即无论起点是什么,信号都可以被及时的传递到该路径的终点,并且在电路正常工作所需的时间段内保持恒定;

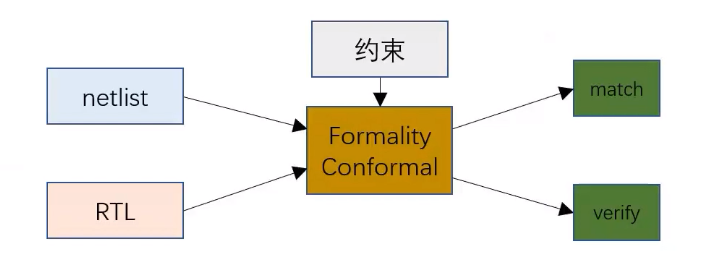

2.2.6 一致性验证

- 输入: RTL代码、网表、约束;

- 输出: match(两张图的节点是否一致)和verify(计算得到的两张图的功能是否一致)的报告;

- 过程: RTL和网表都可以抽象成两幅图,由节点和边组成,中端人员使用Formality、Conformal工具进行一致性验证,采用类似于直接比较两幅图是否一致的方法,来确定网表是否正确。

2.2.7 布局布线

- 布图规划(floor plan): 后端人员使用IC complier、 Encounter等工具进行布局前的规划,目标是优化芯片的面积,时序收敛,稳定,方便走线。是整个后端最重要的一步,也是弹性最大的一步。因为没有标准的最佳方案,但又有很多细节需要考虑。

- 布局: 布局就是摆放标准单元,I/o pad(用于胡须连接芯片引脚),宏单元来实现电路逻辑。布局目标:利用率越高越好,总线越短越好,时序越快越好。但是利用率高布线就困难,总线就长,时序就慢,因此要做个平衡取舍。

- 时钟树综合(clock tree synthesis): 简单说就是时钟的布线,因为时钟信号在数字电路的全局指挥最用,它的分布应该是对称式连接到各个寄存器单元的,从而时钟从一个时钟源到各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。

- 布线: 在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束条件下,根据电路的连接关系,将各单元和I/O pad用互连线连接起来。

2.2.8 生成版图并验证

- 寄生参数提取: 由于导线本身存在电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性的问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次分析验证,分析信号完整性是非常重要的。

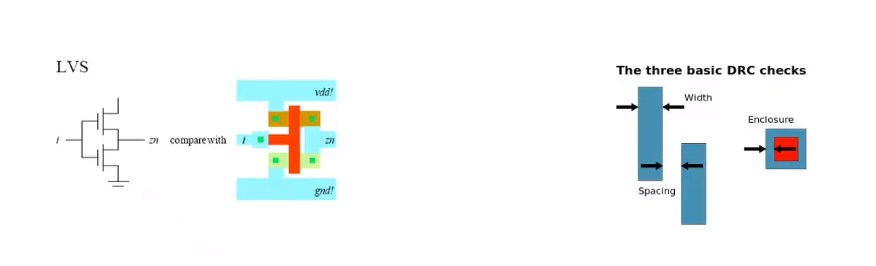

- 生成版图并验证: 对完成布线的物理版图进行功能和时序上的验证,大概包括以下方面: LVS(layout vs schematic)、 DRC(Design Rule Checking)、 ERC(Electrical Rule Checking)